PoP:Package-on-Package Assembly/堆疊封裝

實現(xiàn) 3D 集成的較簡單方案之一,是將已完成封裝的芯片進行堆疊。這類方案的技術名稱中通常包含 “PoP”(即 “封裝堆疊”)。該技術的一個典型應用場景是將 DRAM 芯片堆疊在邏輯芯片上方,臺積電(TSMC)的 InFO 封裝技術中,就包含此類堆疊方案。

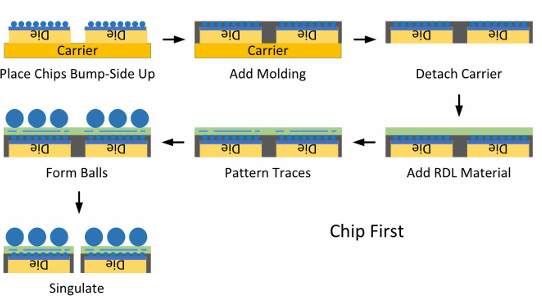

PoP方案的流程為:先將芯片倒扣在載體晶圓上,再進行塑封;移除載體晶圓后,制作重布線層與焊球;最后對重構晶圓進行切割,完成封裝。

CoW:Chip on Wafer Assembly/晶圓級芯片集成

在封裝中實現(xiàn)芯片互連的早期方案之一,是采用晶圓作為載體,并在其上制作重布線層(RDL),臺積電將該技術品牌化為 “CoW”(晶圓級芯片集成)。

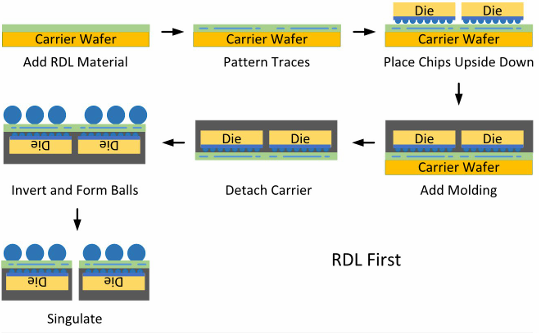

CoW方案的流程為:先在載體晶圓上制作重布線層(RDL),再將預先切割好的芯片(焊凸朝下)放置在載體上;隨后對芯片進行塑封,形成 “重構晶圓”(reconstituted wafer);之后移除載體晶圓,制作焊球,最后對重構晶圓進行切割( singulate),得到獨立封裝體。

英特爾(Intel)的 Foveros 工藝是PoP技術的另一變體,主要用于實現(xiàn)兩顆芯片(或一顆芯片與一個有源中介層)的面對面鍵合。其中,下方芯片需朝上放置,并通過硅通孔(TSV)與基板實現(xiàn)連接。

CoWoS:在CoW方案基礎上加入中介層

前文介紹的方案僅通過重布線層(RDL)實現(xiàn)信號向焊球的布線。若在封裝中加入中介層,則能進一步提升布線靈活性。臺積電的 CoWoS(晶圓級系統(tǒng)集成封裝)是最知名的案例之一,該技術根據(jù)中介層的類型分為三個變體:

①CoWoS-S:采用硅中介層

②CoWoS-R:采用有機材料制作重布線層(無獨立中介層,以有機 RDL 替代中介層功能)

③CoWoS-L:采用小型芯片作為 “布線載體”—— 其結構類似硅橋(silicon bridge),但額外具備通向基板的通孔(vias),可直接與基板連接。